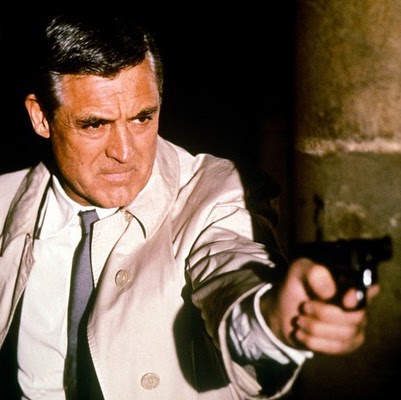

Brian S Cruikshank

age ~58

from Portland, OR

- Also known as:

-

- Brian Scott Cruikshank

- Brian S Crookshank

- Bria Cruikshank

- Bria Crookshank

- Phone and address:

-

9248 NW Murdock St, Portland, OR 97229

303 494-4703

Brian Cruikshank Phones & Addresses

- 9248 NW Murdock St, Portland, OR 97229 • 303 494-4703

- 1917 Ute Creek Dr, Longmont, CO 80504 • 303 834-9578

- 1045 Tantra Park Cir, Boulder, CO 80305 • 303 494-4703

- Aurora, CO

- 1045 Tantra Park Cir, Boulder, CO 80305

Work

-

Position:Service Occupations

Education

-

Degree:High school graduate or higher

License Records

Brian Scott Cruikshank

Address:

9248 NW Murdock St, Portland, OR 97229

License #:

A2838204

Category:

Airmen

Lawyers & Attorneys

Us Patents

-

Alignment Of Parallel Data Channels Using Header Detection Signaling

view source -

US Patent:6829315, Dec 7, 2004

-

Filed:Jan 19, 2000

-

Appl. No.:09/487139

-

Inventors:Brian S. Cruikshank - Boulder CO

-

Assignee:Mindspeed Technologies, Inc. - Newport Beach CA

-

International Classification:H04L 700

-

US Classification:375354, 375364, 375371, 370503, 370506, 341 50, 341102

-

Abstract:A data communication circuit includes a decoder and an alignment buffer. The decoder receives and decodes parallel (N) bit channels into parallel (M+X) bit channels with signaling bits that indicate headers in the parallel (M+X) bit channels. The decoder transfers the parallel (M+X) bit channels to the alignment buffer. The alignment buffer recovers and aligns parallel (M) bit channels using the signaling bits. The alignment buffer generates a clock selection signal using the signaling bits. The alignment buffer transfers the aligned parallel (M) bit channels and the clock selection signal. The alignment buffer can have a length that is a multiple of a frame length for the (M) bit parallel channels.

Resumes

Senior Principal Engineer

view sourceLocation:

Portland, OR

Industry:

Semiconductors

Work:

Ampere

Senior Principal Engineer

Marvell Semiconductor Sep 2010 - Feb 2013

Asic Design Manager

Intel Corporation Sep 2010 - Feb 2013

Technical Lead For Structural Design

Stmicroelectronics Feb 2008 - Sep 2010

Product Marketing Manager

Stmicroelectronics Jan 2004 - Feb 2008

Asic Fe Lead and Design Manager

Senior Principal Engineer

Marvell Semiconductor Sep 2010 - Feb 2013

Asic Design Manager

Intel Corporation Sep 2010 - Feb 2013

Technical Lead For Structural Design

Stmicroelectronics Feb 2008 - Sep 2010

Product Marketing Manager

Stmicroelectronics Jan 2004 - Feb 2008

Asic Fe Lead and Design Manager

Education:

Virginia Tech 1988 - 1992

Master of Science, Masters, Electrical Engineering Virginia Tech 1984 - 1988

Bachelors, Bachelor of Science, Electrical Engineering

Master of Science, Masters, Electrical Engineering Virginia Tech 1984 - 1988

Bachelors, Bachelor of Science, Electrical Engineering

Skills:

Static Timing Analysis

Tcl

Timing Closure

Verilog

Asic

Clock Tree Synthesis

Soc

Dft

Debugging

Fpga

Pcb Design

Rtl Coding

Integrated Circuit Design

System Architecture

Ic

Usb

Logic Synthesis

Microprocessors

Primetime

Rtl Design

Tcl

Timing Closure

Verilog

Asic

Clock Tree Synthesis

Soc

Dft

Debugging

Fpga

Pcb Design

Rtl Coding

Integrated Circuit Design

System Architecture

Ic

Usb

Logic Synthesis

Microprocessors

Primetime

Rtl Design

Design Engineer At Intel Corporation

view sourcePosition:

Design Engineer at Intel Corporation

Location:

Greater Denver Area

Industry:

Semiconductors

Work:

Intel Corporation - Hillsboro, OR since Feb 2013

Design Engineer

Marvell Sep 2010 - Feb 2013

ASIC Design Manager

STMicroelectronics Feb 2008 - Sep 2010

Product Marketing Manager

STMicroelectronics Jan 2004 - Feb 2008

ASIC FE Lead and Design Manager

Fusion Numerics Jan 2003 - Jan 2004

Software Engineer

Design Engineer

Marvell Sep 2010 - Feb 2013

ASIC Design Manager

STMicroelectronics Feb 2008 - Sep 2010

Product Marketing Manager

STMicroelectronics Jan 2004 - Feb 2008

ASIC FE Lead and Design Manager

Fusion Numerics Jan 2003 - Jan 2004

Software Engineer

Education:

Virginia Polytechnic Institute and State University 1988 - 1992

Virginia Polytechnic Institute and State University 1984 - 1988

Virginia Polytechnic Institute and State University 1984 - 1988

Skills:

Static Timing Analysis

TCL

Timing Closure

Verilog

ASIC

Clock Tree Synthesis

SoC

TCL

Timing Closure

Verilog

ASIC

Clock Tree Synthesis

SoC

Plaxo

Brian Cruikshank

view sourceMyspace

Googleplus

Brian Cruikshank

Brian Cruikshank

Classmates

Brian Cruikshank Elizabe...

view sourceBrian Cruikshank 1981 graduate of Elizabeth High School in Elizabeth, NJ is on Memory Lane. Get caught up with Brian and other high school alumni from

Brian Cruikshank Hillsbo...

view sourceBrian Cruikshank 2007 graduate of Hillsborough High School in Tampa, FL is on Memory Lane. Get caught up with Brian and other high school alumni from

Brian Cruikshank

view source

Brian Cruikshank

view source

Brian Cruikshank

view source

Brian Cruikshank

view source

Brian Cruikshank

view source

Brian Cruikshank

view sourceYoutube

Get Report for Brian S Cruikshank from Portland, OR, age ~58