Oleg V Gluschenkov

age ~54

from Poughkeepsie, NY

- Also known as:

-

- Orle Gluschenko

- Oleg Nickolayev

- Luschen G Oleg

- G V

Oleg Gluschenkov Phones & Addresses

- Poughkeepsie, NY

- Tannersville, NY

- Wappingers Falls, NY

- Champaign, IL

- Urbana, IL

- Hopewell Junction, NY

- 16 Fitchett Way, Poughkeepsie, NY 12601

Work

-

Position:Food Preparation and Serving Related Occupations

Education

-

Degree:Associate degree or higher

Us Patents

-

Orientation Independent Oxidation Of Silicon

view source -

US Patent:6358867, Mar 19, 2002

-

Filed:Jun 16, 2000

-

Appl. No.:09/596097

-

Inventors:Helmut Horst Tews - Poughkeepsie NY

Jonathan E. Faltermeir - LaGrange NY

Rajeev Malik - Pleasantville NY

Carol Heenan - LaGrangeville NY

Oleg Gluschenkov - Poughkeepsie NY -

Assignee:Infineon Technologies AG - Munich

International Business Machines Corporation - Armonk NY -

International Classification:H01L 2131

-

US Classification:438771, 438770, 438787, 438788, 438973, 438198

-

Abstract:A method for forming an oxide of substantially uniform thickness on at least two crystallographic planes of silicon, in accordance with the present invention, includes providing a substrate where silicon surfaces have at least two different crystallographic orientations of the silicon crystal. Atomic oxygen (O) is formed for oxidizing the surfaces. An oxide is formed on the surfaces by reacting the atomic oxygen with the surfaces to simultaneously form a substantially uniform thickness of the oxide on the surfaces.

-

Semi-Insulating Diffusion Barrier For Low-Resistivity Gate Conductors

view source -

US Patent:6444516, Sep 3, 2002

-

Filed:Jul 7, 2000

-

Appl. No.:09/613197

-

Inventors:Lawrence Alfred Clevenger - Lagrangeville NY

Jack A. Mandelman - Stormville NY

Rajarao Jammy - Wappinger Falls NY

Oleg Gluschenkov - Poughkeepsie NY

Irene Lennox McStay - Hopewell Junction NY

Kwong Hon Wong - Wappinger Falls NY

Johnathan Faltermeier - Lagrange NY -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:H01L 218234

-

US Classification:438238

-

Abstract:A gate structure for a semiconductor device, and particularly a MOSFET for such applications as CMOS technology. The gate structure entails an electrical insulating layer on a semiconductor substrate, over which a polysilicon gate electrode is formed. The gate structure further includes a gate conductor that is electrically connected with the gate electrode through a diffusion barrier layer having semi-insulating properties. The composition and thickness of the diffusion barrier layer are tailored so that the barrier layer is effective to block diffusion and intermixing between the gate conductor and polysilicon gate electrode, yet provides sufficient capacitive coupling and/or current leakage so as not to significantly increase the gate propagation delay of the gate structure.

-

Method Of Forming Low-Leakage On-Chip Capacitor

view source -

US Patent:6451662, Sep 17, 2002

-

Filed:Oct 4, 2001

-

Appl. No.:09/970635

-

Inventors:Michael Chudzik - Beacon NY

Oleg Gluschenkov - Wappingers Falls NY

Raj Jammy - Wappinger Falls NY

Uwe Schroeder - Dresden, GB

Helmut Tews - Poughkeepsie NY -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:H01L 2120

-

US Classification:438386, 438240, 438393, 438775

-

Abstract:An improved capacitor is formed by a process where an improved node dielectric layer is formed with an improved dielectric constant by performing an Free Radical Enhanced Rapid Thermal Oxidation (FRE RTO) step during formation of the node dielectric layer. Use of an FRE RTO step instead of the conventional furnace oxidation step produces a cleaner oxide with a higher dielectric constant and higher capacitance. Other specific embodiments of the invention include improved node dielectric layer by one or more additional nitridation steps, done by either Remote Plasma Nitridation (RPN), Rapid Thermal Nitridation (RTN), Decoupled Plasma Nitridation (DPN) or other nitridation method; selective oxidation; use of a metal layer rather than a SiN layer as the dielectric base; and selective oxidation of the metal layer.

-

Method Of Improving Gate Activation By Employing Atomic Oxygen Enhanced Oxidation

view source -

US Patent:6566210, May 20, 2003

-

Filed:Jul 13, 2001

-

Appl. No.:09/905233

-

Inventors:Atul C. Ajmera - Wappingers Falls NY

Omer H. Dokumaci - Wappingers Falls NY

Bruce B. Doris - Brewster NY

Oleg Gluschenkov - Wappingers Falls NY -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:H01L 21336

-

US Classification:438303, 438305, 438306, 257344

-

Abstract:The present invention provides a method of preparing a Si-based metal-insulator-semiconductor (MIS) transistor which prevents the polycrystalline grains of the gate conductor from getting significantly larger by reducing the thermal budget of the sidewall oxidation process. The thermal budget of the inventive sidewall oxidation process is reduced one or two orders of magnitude over conventional prior art sidewall oxidation processes by utilizing atomic oxygen as the oxidizing ambient. The present invention also provides Si-based MIS transistors having a gate conductor having grain sizes of about 0. 1, preferably 0. 05, m or less.

-

Method For Forming High Performance Cmos Devices With Elevated Sidewall Spacers

view source -

US Patent:6509221, Jan 21, 2003

-

Filed:Nov 15, 2001

-

Appl. No.:10/000695

-

Inventors:Bruce B. Doris - Brewster NY

Omer H. Dokumaci - Wappingers Falls NY

Oleg Gluschenkov - Wappingers Falls NY -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:H01L 218238

-

US Classification:438199, 438302, 438305

-

Abstract:A method is described for making elevated sidewall spacers on the gate structure of a semiconductor device. A first insulating layer is deposited on the substrate, so that an upper portion of each of the sidewalls extends above the layer. A second insulating layer is deposited on the first layer and on the gate structure. Portions of the second layer disposed on the first layer and on the top surface of the gate structure are removed, so that a remaining portion of the second layer is disposed on the upper portion of each of the sidewalls. The first layer is then removed, so that the remaining portion of the second layer on each of the sidewalls projects laterally therefrom and is elevated with respect to the substrate. This structure is used to implant PFET and NFET extension regions without dose loss.

-

Method Of Enhanced Oxidation Of Mos Transistor Gate Corners

view source -

US Patent:6514843, Feb 4, 2003

-

Filed:Apr 27, 2001

-

Appl. No.:09/844977

-

Inventors:Omer Dokumaci - Wappingers Falls NY

Oleg Gluschenkov - Wappingers Falls NY

Suryanarayan G. Hegde - Hollowville NY

Richard Kaplan - Wappingers Falls NY

Mukesh Khare - White Plains NY -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:H01L 214763

-

US Classification:438595, 438585, 438514, 438766, 438770

-

Abstract:A method of enhancing the rate of transistor gate corner oxidation, without significantly increasing the thermal budget of the overall processing scheme is provided. Specifically, the method of the present invention includes implanting ions into gate corners of a Si-containing transistor, and exposing the transistor including implanted transistor gate corners to an oxidizing ambient. The ions employed in the implant step include Si; non-retarding oxidation ions such as O, Ge, As, B, P, In, Sb, Ga, F, Cl, He, Ar, Kr, and Xe; and mixtures thereof.

-

Method For Forming Junction On Insulator (Joi) Structure

view source -

US Patent:6544874, Apr 8, 2003

-

Filed:Aug 13, 2001

-

Appl. No.:09/928759

-

Inventors:Jack A. Mandelman - Stormville NY

Kevin K. Chan - Staten Island NY

Bomy A. Chen - Ridgefield CT

Oleg Gluschenkov - Wappingers Falls NY

Rajarao Jammy - Wappingers Falls NY

Victor Ku - Tarrytown NY

Chung H. Lam - Williston VT

Nivo Rovedo - LaGrangeville NY -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:H01L 213205

-

US Classification:438589

-

Abstract:A method for forming a JOI structure which allows for reduction in both source/drain junction leakage and capacitance is provided. In the inventive method, an insulator layer is formed under the source/drain regions, but not under the channel region. The insulator layer is formed in the present invention after forming the gate stack region and recessing the semiconductor surface surrounding the gate stack region, followed by deposition of a conductive material such as polysilicon and, optionally, heavy source/drain diffusion formation.

-

Method For Reducing The Microloading Effect In A Chemical Vapor Deposition Reactor

view source -

US Patent:6555166, Apr 29, 2003

-

Filed:Jun 29, 2001

-

Appl. No.:09/895378

-

Inventors:Oleg Gluschenkov - Wappingers Falls NY

Ashima B. Chakravarti - Hopewell Junction NY -

Assignee:International Business Machines - Armonk NY

-

International Classification:C23C 1600

-

US Classification:4272481, 427 8

-

Abstract:A method is provided for reducing the microloading effect in a CVD process for depositing a film on a substrate. This method is particularly useful in a single-wafer CVD reactor. The microloading effect is reduced by identifying a growth-rate-limiting reactant; calculating a dilution factor (the ratio of the gas flow rate of the growth-rate-limiting reactant to the total gas flow rate in the reactor); and adjusting the film growth rate and/or the dilution factor to satisfy a numerical criterion for reducing the microloading effect. The criterion is satisfied when the film growth rate is reduced, or the dilution factor is increased, so that the dilution factor is equal to or greater than a quantity which includes the film growth rate as a factor. The film growth rate and dilution factor may be adjusted independently. The gap between the showerhead and the substrate in the CVD reactor may be adjusted to satisfy the numerical criterion.

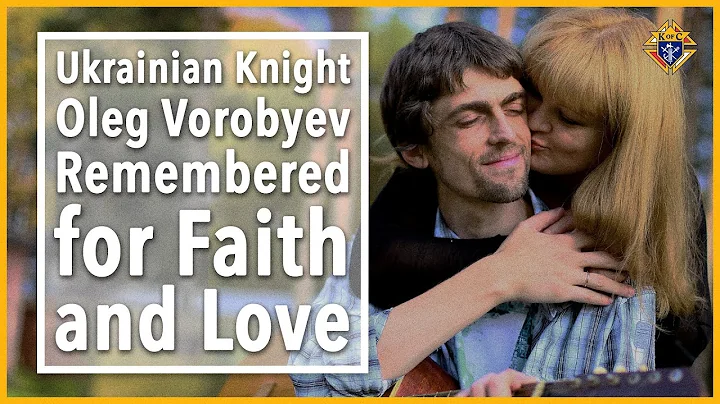

Youtube

Get Report for Oleg V Gluschenkov from Poughkeepsie, NY, age ~54

![[DevOps Speakeasy] Oleg elajev on Graal VM for IoT... [DevOps Speakeasy] Oleg elajev on Graal VM for IoT...](https://i.ytimg.com/vi/lsJiUbq7ars/hq720.jpg?sqp=-oaymwEcCNAFEJQDSFXyq4qpAw4IARUAAIhCGAFwAcABBg==&rs=AOn4CLDXI4ghSDyVgoU82Qe-ARV4fzQBYg)